Journal of Shanghai University >

A conscious fault-tolerant routing algorithm with turn balanced in 3D NoC

Received date: 2018-08-30

Online published: 2018-12-23

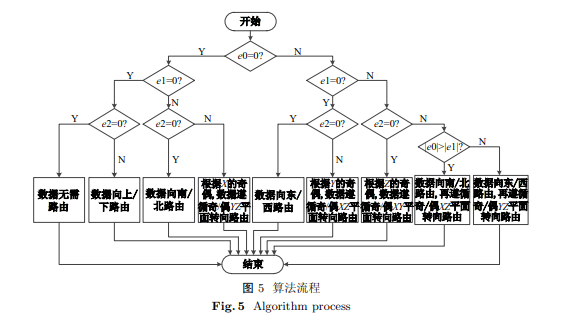

Aiming at the poor performance of adaptive routing strategy and the imperfect fault tolerant mechanism in 3D NoC, the study proposes a perceptually fault-tolerant routing algorithm with turn balanced. Firstly, the XY, XZ and YZ are divided into the odd and even planes and six different forbidden turn directions are established on the row and column to get a more balanced turn model. Then, the horizontal and vertical boundary and internal link fault classification design fault model and fault-tolerant bypass. Finally, the proposed turn and fault model is applied to the routing algorithm combined with the strategy of “full plane 1 hop look-ahead” to improve network performance and fault tolerance. The experimental results show that the proposed algorithm improves throughput by 16.2% and transmission delay by 3.6% when no link failure occurs, and decreases transmission delay by 11.8% at lower link failure rate. With the link failure rate increased, this algorithm still has advantages.

LI Jiao, GUO Runlong, CAI Sheng, CHONG Yunfeng, XU Haipeng, RAN Feng . A conscious fault-tolerant routing algorithm with turn balanced in 3D NoC[J]. Journal of Shanghai University, 2020 , 26(5) : 726 -734 . DOI: 10.12066/j.issn.1007-2861.2081

| [1] | Kim B, Cho S B. Recent advances in TSV inductors for 3D IC technology[C]// SoC Design Conference (ISOCC). 2016: 29-30. |

| [2] | Radfar F, Zabihi M, Sarvari R. Comparison between optimal interconnection network in different 2D and 3D NoC structures[C]// System-on-Chip Conference (SOCC). 2014: 171-176. |

| [3] | Charif A, Coelho A, Zergainoh N E, et al. A dynamic sufficient condition of deadlock-freedom for high-performance fault-tolerant routing in networks-on-chips[J]. IEEE Transactions on Emerging Topics in Computing, 2020,8(3):642-654. |

| [4] | Ahmed A B, Abdallah A B. Adaptive fault-tolerant architecture and routing algorithm for reliable many-core 3D-NoC systems[J]. Journal of Parallel and Distributed Computing, 2016,93:30-43. |

| [5] | Dahir N, Mak T, Yakovlev A. Highly adaptive and deadlock-free routing for three-dimensional networks-on-chip[J]. IET Computers and Digital Techniques, 2013,7(6):255-263. |

| [6] | Chiu G M. The odd-even turn model for adaptive routing[J]. IEEE Transactions on Parallel and Distributed Systems, 2000,11(7):729-738. |

| [7] | Zhou J, Li H, Wang T, et al. LOFT: a low-overhead fault-tolerant routing scheme for 3D NoCs[J]. Integration, 2016,52:41-50. |

| [8] | Zhou J, Li H, Wang T, et al. TURO: a lightweight turn-guided routing scheme for 3D NoCs[C]// 2015 IEEE Symposium in Low-Power and High-Speed Chips. 2015: 1-3. |

| [9] | Lei X, Jiang X, Zeng L, et al. Vertical-mesh-conscious-dynamic routing algorithm for 3D NoCs[C]// IEEE TENCON 2015. 2015:1-6. |

| [10] | Su J, Chai C, Lei X, et al. Vertical-mesh-conscious-dynamic routing algorithm for fault tolerant 3D NoC[C]// IEEE International Conference on Computer and Communications (ICCC). 2016: 2004-2008. |

/

| 〈 |

|

〉 |